## Microstructure and Electrical Properties of III-As Gate Stacks with Amorphous Rare-Earth High-k Oxides

S. Oktyabrsky,\* R. Kambhampati,\* V. Tokranov,\* M. Yakimov,\* T. Heeg,\*\* M. Warusawithana,\*\* D.G. Schlom, \*\* and S. Koveshnikov\*

- \* College of Nanoscale Science and Engineering, University at Albany, Albany, NY 12203

- \*\* Department of Materials Science and Engineering, Cornell University, Ithaca, NY 14853

Integration of group III-V semiconductors, such as InGaAs due to its excellent electron transport properties, with high-k dielectrics is a possible option for the realization of low power, high performance MOSFETs for 15 nm technology node and beyond [1]. Amorphous oxides, such as Ga(Gd)<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub>, have demonstrated so far the best interfaces with GaAs and InGaAs and as a result excellent transistor characteristics, but they have relatively low dielectric constant making scaling difficult. More common, HfO<sub>2</sub> and ZrO<sub>2</sub> gate oxides are typically formed in a polycrystalline form resulting in increased leakage and, possibly, higher trap density due to grain boundaries. Rare-earth ternary oxides (LaAlO<sub>3</sub> or GdScO<sub>3</sub>) have stable amorphous phase up to 1000 <sup>0</sup>C and relatively high dielectric constant (17 and 23, respectively), and are quite promising as novel gate oxides. One of the potential approaches to this gate stack integration involves an amorphous Si interface passivetion layer (IPL) which has proven to reduce interface trap density and gate leakage current, to improve thermal stability of the interface properties and in some cases to reduce the gate oxide charges [2].

The focus of the paper is on correlation of chemistry, microstructure and electrical characteristics of gate stacks with amorphous rare-earth oxides and Si IPL on GaAs and InGaAs and there thermal stability, which is essential in MOSFET processing. The gate stacks were fabricated using molecular beam epitaxy (MBE) and in-situ deposition of amorphous Si IPL and quasi-in-situ (with protection layer deposition and desorption) MBE of high-k oxides [3]. TEM with EDX and EELS accompanied with XPS was used for microstructural and chemical analysis, and capacitance-voltage and transistor characteristics were measured on processed test structures.

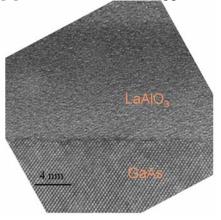

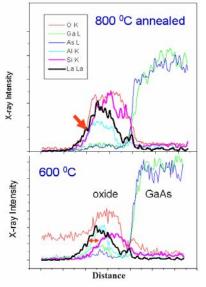

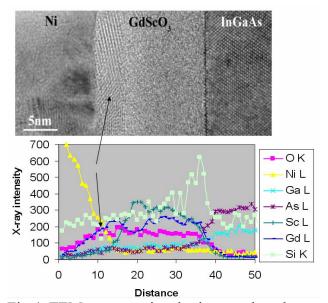

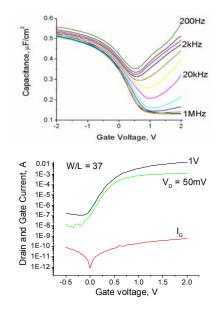

The LaAlO<sub>3</sub>/GaAs stack with a-Si IPL (which is oxidized within process flow) exhibited not only excellent thermal stability of the electrical and structural properties up to 800 °C (Figs. 1-3), but demonstrated a reduction of EOT by ~50% (Fig. 3) with annealing, 20-fold reduction of hysteresis, and interface state density as low as  $2\times10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> [3]. Oxidation of the Si IPL were studied to ensure that no covalent Si is available for diffusion into semiconductor [4]. The observed dissolving of low-k SiO<sub>x</sub> layer into LaAlO<sub>3</sub> at higher temperatures (Fig.2) can explain increasing of accumulation capacitance and reduction of the equivalent oxide thickness (EOT) with annealing shown in the Fig. 3. Similarly, excellent thermal stability is found in the GdScO<sub>3</sub>/SiO<sub>x</sub>/InGaAs/InP stack (Fig. 4,5). Although the GdScO<sub>3</sub>/SiO<sub>x</sub> interface appears very stable, the Ni/GdScO<sub>3</sub> interface has shown catalytically-induced Gd<sub>2</sub>O<sub>3</sub> crystallization with associated GdScO<sub>3</sub> phase separation (Fig. 4). This gate stack demonstrated record low frequency dispersion (< 5%/dec.) in accumulation for InGaAs channel material (Fig. 5), reduced fixed oxide charge leading to a positive shift (~0.5V) of flat band voltage, reduced interface trap density close to the valence band, although Dit was higher at midgap. All the gate stacks with a-Si IPL have shown significant reduction of gate leakage current after annealing. Fig. 5(bottom) shows input characteristics of enhancement mode InGaAs/InP n-MOSFET ( $V_T$ =0.3 V) with subthreshold slope of 130 mV/dec., Ion/Ioff ~  $10^5$ , and channel resistance in the linear region 1.5 k $\Omega$ /sq. [5].

## References

- [1] R. Chau, S. Datta, and A. Majumdar, IEEE CSICS-2005, Tech. Digest, (2005)17-20.

- [2] S. Oktyabrsky, et al., Materials Sci. Eng. B, 135 (2006) 272.

- [3] S. Koveshnikov, et al., Appl. Phys. Lett. 93 (2008) 012903.

- [4] R. Kambhampati, et al. ECS Trans. 11 (2007) 431.

- [5] This research was supported by the SRC/MARCO MSD Focus Center and Intel Corporation.

Fig.1. TEM micrograph of the interface LaAlO<sub>3</sub>/SiO<sub>x</sub>/GaAs with a fully oxidized 1.5 nm thick *a*-Si layer after 800°C anneal. Oxide is amorphous with clean interface.

Fig.2. Cross-sectional EDX profiles of interface in Fig.1 after at 600 and 800°C annealing.

Fig. 3. Top: Effect of annealing on the *C-V* characteristics of gate stack in Fig. 1. Bottom: Contribution of the *a*-Si to EOT.

Fig.4. TEM cross-sectional micrograph and EDX profile of the  $GdScO_3/SiO_x/InGaAs$  gate stack after 800  $^0C$  annealing.

Fig. 5. Top: C-V characteristics of Ni/GdScO<sub>3</sub>/SiO<sub>x</sub>/p-InGaAs MOS structures with Si IPL; and bottom: MOSFET input characteristics.